Designing better ways to design better electronics

Electronic systems are everywhere. They closely interact with the physical systems they are embedded in, with human users, and with other systems connected in networks. Electronic systems are how we are going to create a smart society – if we can solve the societal challenges of reliability, miniaturization and reduction of power dissipation. The Electronic Systems (ES) research group aims to provide a scientific basis for design trajectories for electronic systems, from function to realization, and to do so in collaboration with industry.

Read moreOur subprograms

The ES research program targets the design of next generations of electronic systems. It is organized in three subprograms that cover the engineering, system and circuit perspectives. This allows an integral approach to the design of electronic systems.

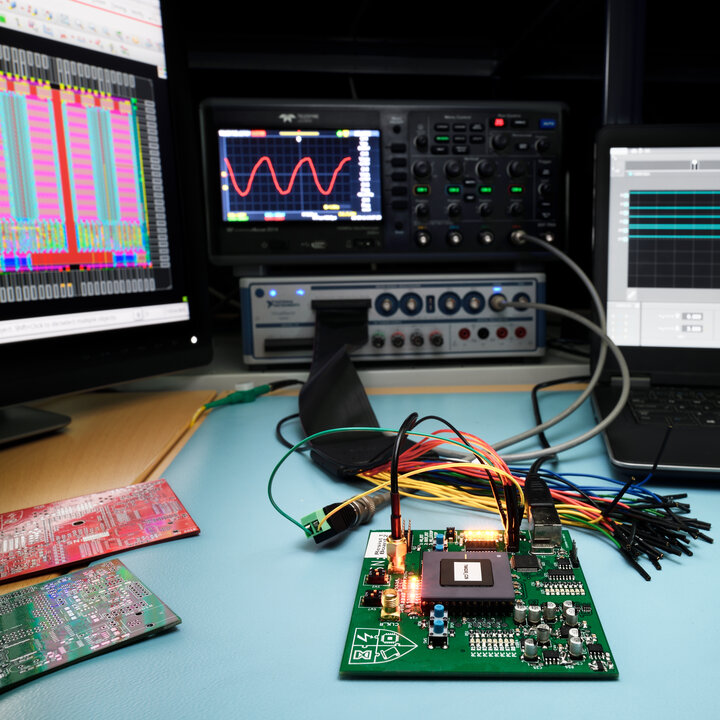

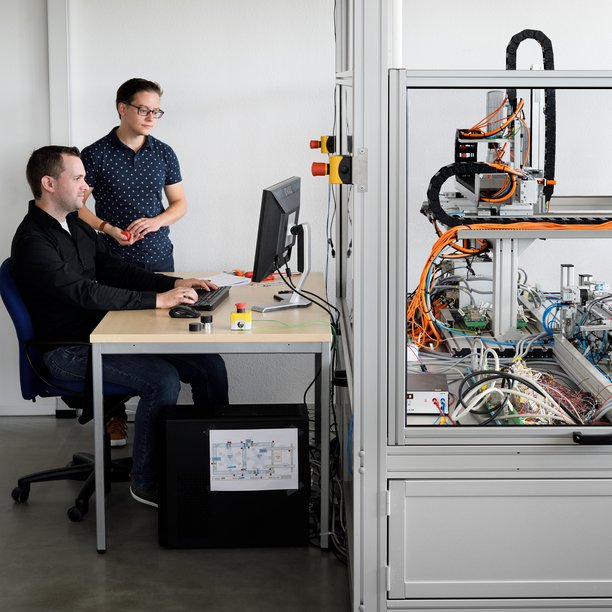

Our Labs

News

![[Translate to English:] [Translate to English:]](https://assets.w3.tue.nl/w/fileadmin/_processed_/7/f/csm_BvOF%2001%20kickoff%20Future%20Chips%20Academy%20-%20group%20photo_5396222a83.jpg)

Highlighted projects

Research highlight: Machine Learning

Machine learning and in particular deep learning (DL) has dramatically improved the state-of-the-art in object detection, speech recognition, robotics, and many other domains. Whether it is superhuman performance in object recognition or beating human players in Go, the astonishing success of deep learning is achieved by deep neural networks trained with huge amounts of training examples and massive computing resources. Although already applied successfully in academic use-cases and several consumer products (e.g. machine translation), these data and computing requirements pose challenges for further market penetration. Efficient Deep Learning (EDL) is an important focus point of our Smart Electronic Systems and Digital Nanoelectronics subprograms.

Read moreMeet some of our Researchers

WORK WITH US!

All scientific as well as non-scientific vacancies are centrally cataloged by the Electrical Engineering department and can be found here.

We are always looking for exceptional candidates interested in pursuing a PhD. So if you have (almost completed) a Master's degree in Electrical Engineering, Computer Engineering, Computer Science, or a related area, and if you have expertise and interest in one or more relevant areas, e.g., digital circuits, VLSI, design automation, multiprocessor systems-on-chip, models of computation, compiler technology, embedded systems, IoT, or CPS, you are invited to apply.

Recent Publications

Our most recent peer reviewed publications

-

Zohreh Hosseinkhani,Majid Nabi

BMSim

IEEE Internet of Things Journal (2024) -

Raquel Pires Alves,Fokke van Meulen,M.J.H. van Gastel,Wim Verkruysse,Sebastiaan Overeem,Sveta Zinger,Sander Stuijk

Thermal Imaging for Respiration Monitoring in Sleeping Positions

(2024) -

Floran de Putter,M.D. Gomony,Pekka Jääskeläinen,Henk Corporaal

BrainTTA

(2023) -

Marzieh Hashemipour-Nazari,Yuqing Ren,Kees Goossens,Alexios Balatsoukas-Stimming

Pipelined Architecture for Soft-Decision Iterative Projection Aggregation Decoding for RM Codes

IEEE Transactions on Circuits and Systems I: Regular Papers (2023) -

Joachim Tapparel,Alexios Balatsoukas-Stimming,Andreas Burg

LoRa Preamble Detection Robust to Inter-channel Interference

(2023)

Contact

-

Visiting address

FluxGroene Loper 195612 AP EindhovenNetherlands -

Visiting address

FluxGroene Loper 195612 AP EindhovenNetherlands -

Postal address

P.O. Box 513Department of Electrical Engineering5600 MB EindhovenNetherlands -

Postal address

P.O. Box 513Department of Electrical Engineering5600 MB EindhovenNetherlands -

Secretary