|

Théodore Marescaux |

|

Théodore Marescaux |

| [1] |

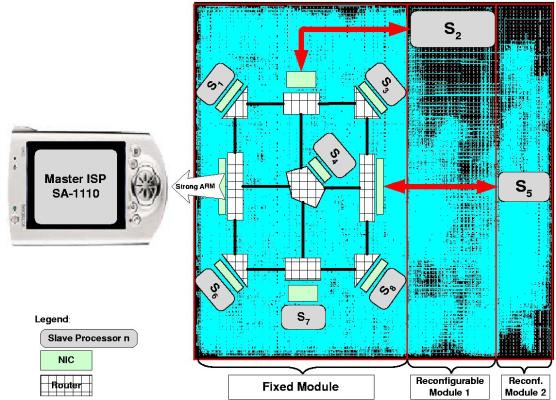

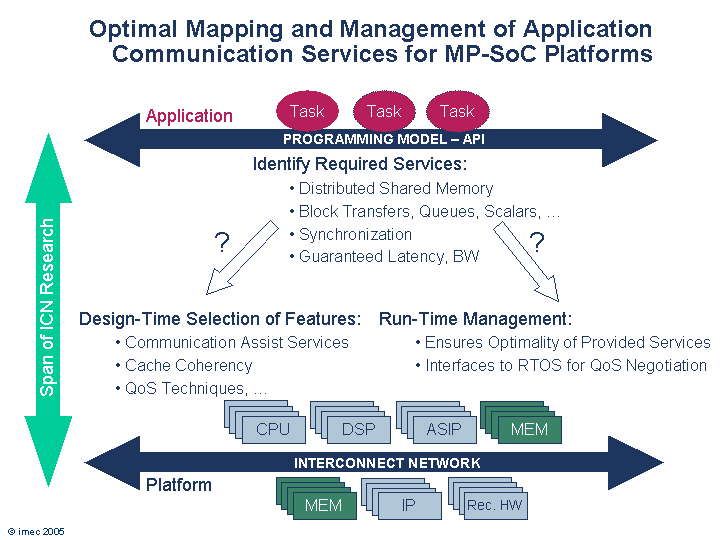

V. Nollet, T. Marescaux, D. Verkest, J-Y. Mignolet, and S. Vernalde.

Operating System controlled Network-on-Chip.

In Proceedings of the Design Automation Conference

(DAC04), pages 256-259, June 2004.

San Diego. [ bib ] |

| [2] |

T.A. Bartic, D. Desmet, J-Y. Mignolet, T. Marescaux, D. Verkest, S. Vernalde,

R. Lauwereins, J. Miller, and F. Robert.

Network-on-Chip for Reconfigurable Systems: From

High-Level Design Down to Implementation.

In Field Programmable Logic and Application, volume

3203/2004 of Lecture Notes in Computer Science, pages 637-647.

Springer Berlin / Heidelberg, 2004. [ bib ] |

| [3] |

T.A. Bartic, J.-Y. Mignolet, V. Nollet, T. Marescaux, D. Verkest, S. Vernalde,

and R. Lauwereins.

Topology adaptive network-on-chip design and implementation.

In Computers and Digital Techniques, IEE Proceedings,

volume 152, pages 467- 472, July 2005. [ bib ] |

| [4] |

T.A. Bartic, J.-Y. Mignolet, V. Nollet, T. Marescaux, D. Verkest, S. Vernalde,

and R. Lauwereins.

Highly scalable network on chip for reconfigurable systems.

In System-on-Chip, 2003. Proceedings. International

Symposium on, pages 79- 82, 2003. [ bib ] |

| [5] |

Theodore Marescaux, Andrei Bartic, Dideriek Verkest, Serge Vernalde, and Rudy

Lauwereins.

Interconnection Networks Enable Fine-Grain Dynamic

Multi-tasking on FPGAs.

In Field-Programmable Logic and Applications.

Reconfigurable Computing Is Going Mainstream 12th International

Conference, FPL 2002, Montpellier, France September 2-4, 2002.

Proceedings, volume 2438/2002 of Lecture Notes in Computer Science,

pages 795-804. Springer Berlin / Heidelberg, 2002. [ bib ] |

| [6] |

Theodore Marescaux, Benjamin Bricke, Peter Debacker, Vincent Nollet Nollet, and

Henk Corporaal.

Dynamic Time-Slot Allocation for QoS Enabled Networks

on Chip.

In Proc. IEEE 3rd Workshop on Embedded Systems for

Real-Time Multimedia (ESTIMedia), pages 47-52, New York, USA, 09

2005. IEEE. [ bib ] |

| [7] |

T. Marescaux, J-Y. Mignolet, A. Bartic, W. Moffat, D. Verkest, S. Vernalde, and

R. Lauwereins.

Networks on Chip as Hardware Components of an OS for

Reconfigurable Systems.

In Field-Programmable Logic and Applications, volume

2778/2003 of Lecture Notes in Computer Science, pages 595-605.

Springer Berlin / Heidelberg, 2003. [ bib ] |

| [8] |

T. Marescaux, V. Nollet, J.-Y. Mignolet, A. Bartic, W. Moffat, P. Avasare,

P. Coene, D. Verkest, S. Vernalde, and R. Lauwereins.

Run-time support for heterogeneous multitasking on reconfigurable

SoCs.

Integr. VLSI J., 38(1):107-130, 2004. [ bib ] |

| [9] |

Theodore Marescaux, Anders Rångevall, Vincent Nollet, Andrei Bartic, and

Henk Corporaal.

Distributed congestion control for packet switched networks on chip.

In Parallel Computing Conference (ParCo 2005),

Proceedings, Malagà, Spain, 09 2005. [ bib ] |

| [10] |

V. Nollet, T. Marescaux, P. Avasare, and J-Y. Mignolet.

Centralized Run-Time Resource Management in a

Network-on-Chip Containing Reconfigurable Hardware Tiles.

In DATE '05: Proceedings of the conference on Design,

Automation and Test in Europe, pages 234-239, Washington, DC, USA,

2005. IEEE Computer Society. [ bib ] |