Lines starting with "$"

indicate commands entered in cygwin bash prompt.

1 Install X-Win32

1. You will need X terminal software called X-Win32 that

allows PC users to connect their Microsoft Windows systems to

powerful X Window System applications residing on Unix-based

servers. You may download X-win32 from

NUS

web shopping.

2.

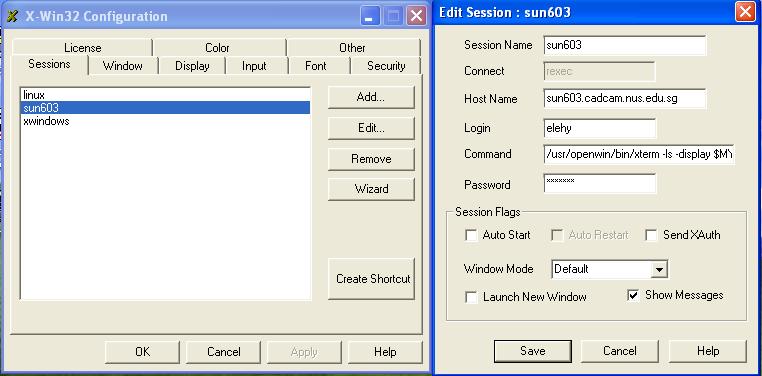

After the installation, you have to run Start->All

Programs->X-Win32 5.4-> X-Config to configure the X terminal

settings. An example GUI is shown below.

3.

click add button to add your configuration for one session.

4. choose rexec as the connect method.

5. fill the following info as requested:

Session Name: any name you prefer.

Host Name: sun603.cadcam.nus.edu.sg

Login: use the username that cad/cam center allocates to

you.

Command: /usr/openwin/bin/xterm -ls -display $MYIP:$DNUM

Password: use the password that cad/cam center allocates to

you.

Leave the rest as default value and click Save.

6. run Start -> All programs -> X-Win32 and you will see it

showing as

on the right bottom corner of your screen.

7. right click the icon and choose the X session you have

configured. The following X terminal will appear.

8. Now you are ready to execute Unix commands using this xterm.

1. Replace the .cshrc file in your Unix home directory with the

one here.

2. run "$ source .cshrc" to make the changes effective. 3. run

"which dc_shell" to see if the setting is correct. If correct, you

should see: /app11/synopsys/synthesis/sparcOS5/syn/bin/dc_shell 4. Download the file synt.exe from here

and unpack it. This package contains an example ALU project file which we

need to test the CoCentric compiler. 5. Transfer the extracted

directory from your Windows machine to your Unix account. 6. Change the current directory to

the directory with ALU project file, e.g. $ cd mips/alu

(suppose you have unpacked your file to the directory of mips.)

Example session to compile the ALU project. 1. Change to the directory with SystemC sources $ cd /staff1/elehy/mips/alu

2. Make sure that cocentric.scr file and all .cpp and .h files

are present in the directory

3. Launch cocentric $ dc_shell -f cocentric

The sources will be compiled with the script cocentric.scr

Behavioral Compiler (TM)

DC Professional (TM)

DC Expert (TM)

DC Ultra (TM)

VHDL Compiler (TM)

HDL Compiler (TM)

Library Compiler (TM)

Power Compiler (TM)

DFT Compiler (TM)

BSD Compiler

DesignWare Developer (TM)

DesignPower (TM)

Version 2002.05-SP2 for linux -- Nov 15, 2002

Copyright (c) 1988-2002 by Synopsys, Inc.

ALL RIGHTS RESERVED

This program is proprietary and confidential information of Synopsys, Inc.

and may be used and disclosed only as authorized in a license agreement

controlling such use and disclosure.

Initializing...

----- File alu.cpp

CoCentric(R) SystemC Compiler -- Version 2002.05-SP2 (Thu Oct 17 12:56:17 PDT

02)

Copyright (c) 1999-2001 by Synopsys, Inc. ALL RIGHTS RESERVED.

Information: Reading source file `/home/s654321/sc/alu.cpp' (SCC-171)

OK

----- File bin2seg.cpp

CoCentric(R) SystemC Compiler -- Version 2002.05-SP2 (Thu Oct 17 12:56:17 PDT

02)

Copyright (c) 1999-2001 by Synopsys, Inc. ALL RIGHTS RESERVED.

Information: Reading source file `/home/s654321/sc/bin2seg.cpp' (SCC-171)

Information at bin2seg.cpp:35: Full-case automatically detected. (SCC-179)

OK

----- File dip.cpp

CoCentric(R) SystemC Compiler -- Version 2002.05-SP2 (Thu Oct 17 12:56:17 PDT

02)

Copyright (c) 1999-2001 by Synopsys, Inc. ALL RIGHTS RESERVED.

Information: Reading source file `/home/s654321/sc/dip.cpp' (SCC-171)

OK

----- File led.cpp

CoCentric(R) SystemC Compiler -- Version 2002.05-SP2 (Thu Oct 17 12:56:17 PDT

02)

Copyright (c) 1999-2001 by Synopsys, Inc. ALL RIGHTS RESERVED.

Information: Reading source file `/home/s654321/sc/led.cpp' (SCC-171)

OK

----- File split.cpp

CoCentric(R) SystemC Compiler -- Version 2002.05-SP2 (Thu Oct 17 12:56:17 PDT

02)

Copyright (c) 1999-2001 by Synopsys, Inc. ALL RIGHTS RESERVED.

Information: Reading source file `/home/s654321/sc/split.cpp' (SCC-171)

OK

----- File top.h

CoCentric(R) SystemC Compiler -- Version 2002.05-SP2 (Thu Oct 17 12:56:17 PDT

02)

Copyright (c) 1999-2001 by Synopsys, Inc. ALL RIGHTS RESERVED.

Information: Reading source file `/home/s654321/sc/top.h' (SCC-171)

OK

dc_shell>

Thank you...

Finally, the resulting verilog files will be transferred back

to the subdirectory v in the current directory ALU.v 100% |*****************************| 1254 00:00

BIN2SEG.v 100% |*****************************| 1126 00:00

DIP.v 100% |*****************************| 1187 00:00

LED.v 100% |*****************************| 369 00:00

SPLIT.v 100% |*****************************| 432 00:00

TESTBENCH.v 100% |*****************************| 970 00:00

Use FPGA CompilerII Design Wizard to compile the verilog files

for the correct FPGA device, using module TESTBENCH as the top-level

module. For detailed instructions, see here

Return to the project's main directory (~/mips/alu) Make sure files MapEdif.bat and TESTBENCH.ucf

are present in this directory. Copy EDIF file created by FPGA

CompilerII to the current directory. The EDIF file is in the FCII

project directory, created as a subdirectory of verilog source

directory v. $ cp v/TESTBENCH_fc2_proj/TESTBENCH.edf .

Invoke MapEdif.bat script with the EDIF file name (no

extension!). If you encounter the message 'XILINX variable not set',

set the Windows environment variable XILINX to point to your Webpack

installation (e.g. c:\xilinx_webpack). You can set a

Windows variable through Control Panel, icon System, tab Advanced,

button Environment Variables, select "New..." and type variable name

and value. Then, restart the cygwin shell. $ ./MapEdif.bat TESTBENCH

############ Processing TESTBENCH.edf ##############

----- EDIF TO NGD -----

Release 3.3WP8.x - ngdbuild D.27

Copyright (c) 1995-2000 Xilinx, Inc. All rights reserved.

Command Line: ngdbuild -dd __ngo -nt timestamp -sd

c:\xilinx_webpack\Spartan2\data\map -p 2S200-PQ208-5 -uc TESTBENCH.ucf

TESTBENCH.edf TESTBENCH.ngd

Launcher: Executing edif2ngd "TESTBENCH.edf" "__ngo\TESTBENCH.ngo"

Release 3.3WP8.x - edif2ngd D.27

Copyright (c) 1995-2000 Xilinx, Inc. All rights reserved.

Writing the design to "__ngo/TESTBENCH.ngo"...

Reading NGO file "d:/Ogo1.2/mips/alu/__ngo/TESTBENCH.ngo" ...

Reading component libraries for design expansion...

Annotating constraints to design from file "TESTBENCH.ucf" ...

Checking timing specifications ...

Checking expanded design ...

NGDBUILD Design Results Summary:

Number of errors: 0

Number of warnings: 0

Writing NGD file "TESTBENCH.ngd" ...

Writing NGDBUILD log file "TESTBENCH.bld"...

NGDBUILD done.

----- Mapping -----

Release 3.3WP8.x - Map D.27

Copyright (c) 1995-2000 Xilinx, Inc. All rights reserved.

Using target part "2s200pq208-5".

Reading NGD file "TESTBENCH.ngd"...

Processing FMAPs...

Removing unused or disabled logic...

Running cover...

Writing file TESTBENCH.ngm...

Running directed packing...

Running delay-based packing...

Running related packing...

Writing design file "TESTBENCH.ncd"...

Design Summary:

Number of errors: 0

Number of warnings: 4

Number of Slices: 51 out of 2,352 2%

Number of Slices containing

unrelated logic: 0 out of 51 0%

Number of 4 input LUTs: 100 out of 4,704 2%

Number of bonded IOBs: 44 out of 140 31%

Total equivalent gate count for design: 789

Additional JTAG gate count for IOBs: 2,112

Removed Logic Summary:

61 block(s) optimized away

Mapping completed.

See MAP report file "TESTBENCH.mrp" for details.

1 file(s) copied.

----- Place and Route -----

Release 3.3WP8.x - Par D.27

Copyright (c) 1995-2000 Xilinx, Inc. All rights reserved.

Constraints file: TESTBENCH.pcf

Loading design for application par from file TESTBENCH_map.ncd.

"TESTBENCH" is an NCD, version 2.35, device xc2s200, package pq208, speed -5

Loading device for application par from file 'v200.nph' in environment

c:/xilinx_webpack.

Device speed data version: ADVANCED 1.21 2001-04-09.

Resolving physical constraints.

Finished resolving physical constraints.

Device utilization summary:

Number of External IOBs 44 out of 140 31%

Number of SLICEs 51 out of 2352 2%

Overall effort level (-ol): 2 (set by user)

Placer effort level (-pl): 2 (set by user)

Placer cost table entry (-t): 1

Router effort level (-rl): 2 (set by user)

Starting the placer. REAL time: 0 secs

Placement pass 1 .

Placer score = 17685

Optimizing ...

Placer score = 16455

All IOBs have been constrained to specific sites.

Placer completed in real time: 0 secs

Dumping design to file TESTBENCH.ncd.

Total REAL time to Placer completion: 0 secs

Total CPU time to Placer completion: 1 secs

0 connection(s) routed; 328 unrouted.

Starting router resource preassignment

Completed router resource preassignment. REAL time: 0 secs

Starting iterative routing.

Routing active signals.

.....

End of iteration 1

328 successful; 0 unrouted; (0) REAL time: 0 secs

Constraints are met.

Total REAL time: 0 secs

Total CPU time: 1 secs

End of route. 328 routed (100.00%); 0 unrouted.

No errors found.

Completely routed.

This design was run without timing constraints. It is likely that much better

circuit performance can be obtained by trying either or both of the following:

- Enabling the Delay Based Cleanup router pass, if not already enabled

- Supplying timing constraints in the input design

Total REAL time to Router completion: 0 secs

Total CPU time to Router completion: 1 secs

Generating PAR statistics.

Dumping design to file TESTBENCH.ncd.

All signals are completely routed.

Total REAL time to PAR completion: 2 secs

Total CPU time to PAR completion: 1 secs

Placement: Completed - No errors found.

Routing: Completed - No errors found.

PAR done.

----- Bitgen -----

Release 3.3WP8.x - Bitgen D.27

Copyright (c) 1995-2000 Xilinx, Inc. All rights reserved.

Loading design for application Bitgen from file TESTBENCH.ncd.

"TESTBENCH" is an NCD, version 2.35, device xc2s200, package pq208, speed -5

Loading device for application Bitgen from file 'v200.nph' in environment

c:/xilinx_webpack.

Opened constraints file TESTBENCH.pcf.

Fri Jan 10 13:39:48 2003

Running DRC.

DRC detected 0 errors and 0 warnings.

Creating bit map...

Saving bit stream in "testbench.bit".

----- Timing report -----

Release 3.3WP8.x - Trace D.27

Copyright (c) 1995-2000 Xilinx, Inc. All rights reserved.

Loading design for application trce from file testbench.ncd.

"TESTBENCH" is an NCD, version 2.35, device xc2s200, package pq208, speed -5

Loading device for application trce from file 'v200.nph' in environment

c:/xilinx_webpack.

--------------------------------------------------------------------------------

Xilinx TRACE, Version D.27

Copyright (c) 1995-2000 Xilinx, Inc. All rights reserved.

c:/xilinx_webpack/bin/nt/trce -v TESTBENCH.ncd

Design file: testbench.ncd

Physical constraint file: testbench.pcf

Device,speed: xc2s200,-5 (ADVANCED 1.21 2001-04-09)

Report level: verbose report

--------------------------------------------------------------------------------

WARNING:Timing:2491 - No timing constraints found, doing default enumeration.

Timing summary:

---------------

Timing errors: 0 Score: 0

Constraints cover 2050 paths, 126 nets, and 328 connections (100.0% coverage)

Design statistics:

Maximum combinational path delay: 26.604ns

Maximum net delay: 5.762ns

Analysis completed Fri Jan 10 13:39:53 2003

--------------------------------------------------------------------------------

Total time: 2 secs

"Timing report written to TESTBENCH.twr"

In the current directory, among other files, file

testbench.bit (FPGA programming file) is created. Make sure that

FPGA device is connected to the parallel port and switched on.

Launch JTAG Device Programmer, select File/Initialize Chain,

double-click on the XCV200 device that appears in the window, select

in the dialog box that appears the testbench.bit file, and finally

select Operations/Program to program the device. |