# Challenges and Solutions for Consumer Flash-Memory Devices

Tei-Wei Kuo, Po-Chun Huang, and Yuan-Hao Chang Dept. of Computer Science & Info. Engr. National Taiwan University, Taiwan IIS and CITI, Academia Sinica, Taiwan

Tei-Wei Kuo, NTU, All Rights Reserved

-

## Agenda

- Introduction

- Architecture and Design Issues

- Performance Issues

- Reliability/Endurance Issues

- Conclusion

2011/10/10

Tei-Wei Kuo, NTU, All Rights Reserved

### Introduction

- Diversified Application Domains

- Portable Storage Devices

- Consumer Electronics

- Servers and Storage Systems

- Industrial Applications

2011/10/10

Tei-Wei Kuo, NTU, All Rights Reserved

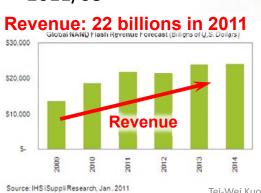

### Trends - Market Growth

#### Mobile Devices

- Smartphones: 50%+ of growth from 2010/02 to 2011/05

- Tablet PCs, e.g., iPad

- Automotive navigation systems

#### Flash Memory

25% growth from 2011/01 to 2011/08

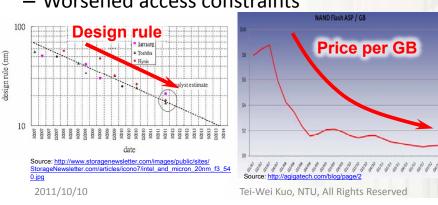

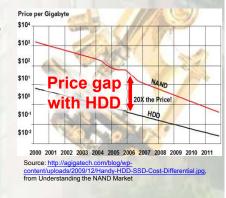

#### Trends - Market and Technology

#### Competitiveness in the Price

- Dropping Rate and the Price Gap with HDDs

- Technology Trend over the Market

- Improved density

- Degraded performance

- Degraded reliability

- Worsened access constraints

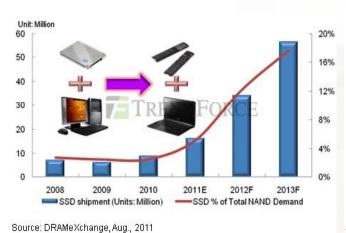

## Trends – Solid-State Disks (SSDs)

- Flourishing in SSD Developments

- Top 20 Vendors in 2010Q4: Fusion-io, SandForce, STEC, Violin Memory, Texas Memory Systems, OCZ, WD Solid State Storage, Pliant Technology, SanDisk, RunCore, ForeMay, Intel, Toshiba, SMART Modular Technologies, Seagate, Virident Systems, Kove, EMC, BiTMICRO, and DDRdrive

Toshiba's Roadmap for SSD Products

2007 (56nm) 2008 (43nm) 2009 (33nm)

Using the same forms as of the HDDs / Realizing a 5126B SSD

Module Type

(70.6x53.6x3mm) 128GB

256GB 512GB

512GB

128GB 256GB

512GB

128GB

128

## Agenda

- Introduction

- Architecture and Design Issues

- Performance Issues

- Reliability/Endurance Issues

- Conclusion

2011/10/10

Tei-Wei Kuo, NTU, All Rights Reserved

# The Characteristics of Different Storage Media

| Media               | Access time                    |                                                    |                                   |  |  |

|---------------------|--------------------------------|----------------------------------------------------|-----------------------------------|--|--|

|                     | Read                           | Write                                              | Erase                             |  |  |

| DRAM                | 13.9ns (1B)<br>7.12us (512B)   | 13.9ns (1B)<br>7.12us (512B)                       | N/A                               |  |  |

| NOR Flash           | 45ns (1B)<br>23.0us (512B)     | 14us (1B)<br>7.2ms (512B)                          | 18ms (128KB)                      |  |  |

| PCM                 | 115—135 ns (1B)<br>13us (512B) | 115—135 ns (1B)<br>13us (512B)                     | N/A                               |  |  |

| NAND Flash<br>(SLC) | 15us (1B)<br>MAX: 35us (8KB)   | 300us (1B)<br>TYP: 350us (8KB)<br>MAX: 500us (8KB) | TYP: 1.5ms (1MB)<br>MAX:3ms (1MB) |  |  |

| DISK                | 15.8ms<br>TYP: 8.2ms (512B)    | 6.06ms<br>TYP: 9.2ms (512B)                        | N/A                               |  |  |

Reference Devices/Modules: DRAM: Micron DDR3-1333. NOR Flash: Silicon Storage Technology SST39LF020. PCM: Micron P8P Parallel PCM, NAND Flash: Micron MT29F256G08AUAAAC5. Disk: Deskstar™ 7K3000 series.

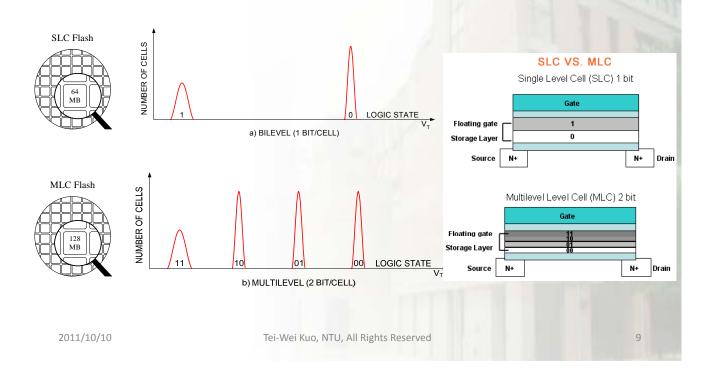

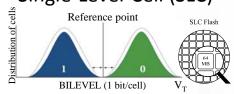

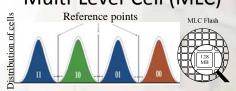

## Single Level Cell (SLC) vs Multi-Level Cell (MLC)

## Single-Level Cell (SLC)

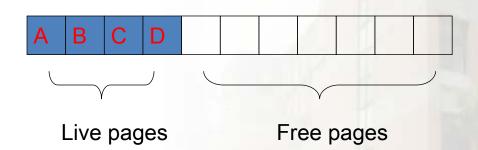

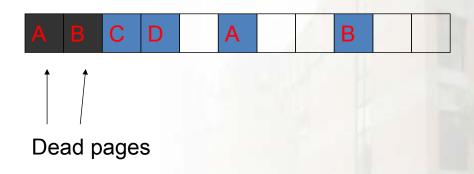

Example 1: Out-place Update

Suppose that we want to update data A and B...

2011/10/10

Tei-Wei Kuo, NTU, All Rights Reserved

13

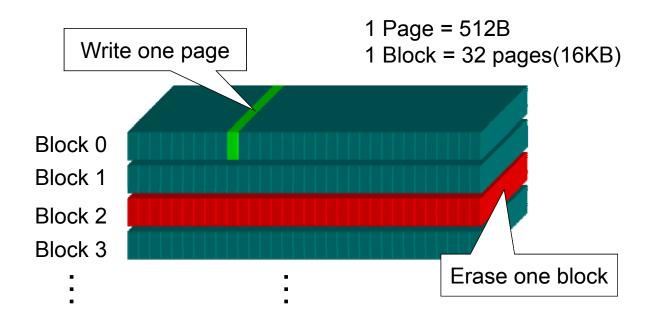

## Management Issues – Flash-Memory Characteristics

Example 1: Out-place Update

2011/10/10

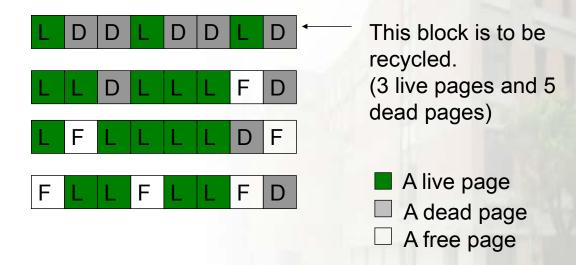

Example 2: Garbage Collection

2011/10/10

Tei-Wei Kuo, NTU, All Rights Reserved

14

## Management Issues – Flash-Memory Characteristics

Example 2: Garbage Collection

2011/10/10

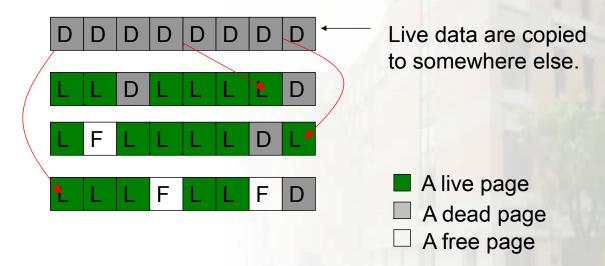

Example 2: Garbage Collection

The block is then erased.

Overheads:

- live data copying

- ·block erasing.

- A live page

- ☐ A dead page

- A free page

2011/10/10

Tei-Wei Kuo, NTU, All Rights Reserved

1

## Management Issues – Flash-Memory Characteristics

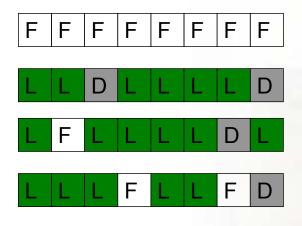

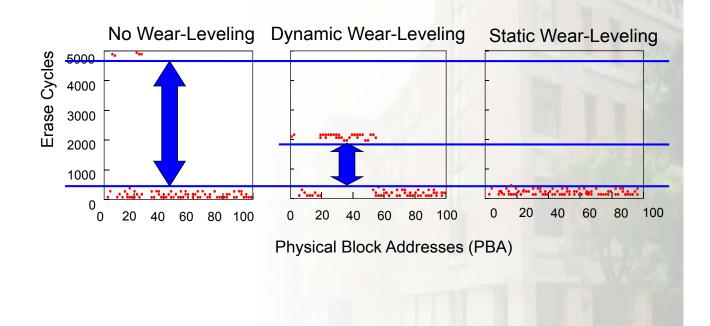

Example 3: Wear-Leveling

Wear-leveling might interfere with the decisions of the block-recycling policy.

- A live page

- A dead page

- ☐ A free page

Erase cycle counts

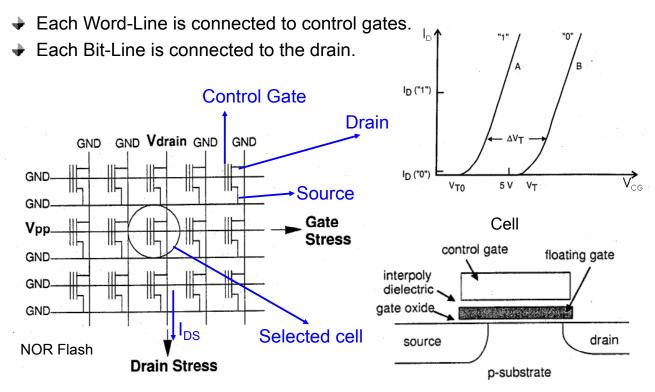

#### SLC Flash Access Constraints

- Write-Once

- · No writing on the same page unless its residing block is erased!

- Pages are classified as valid, invalid, and free pages.

- Bulk-Erasing

- Pages are erased in a block unit to recycle used but invalid pages.

- Wear-Leveling

- Each block has a limited lifetime in erasing counts.

#### Additional MLC Flash Access Constraints

- Prohibition of partial page programming

- Serial page programming in a block

2011/10/10

Tei-Wei Kuo, NTU, All Rights Reserved

1.0

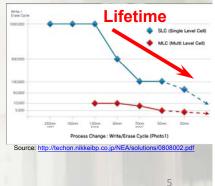

## Comparisons of SLC and MLC

- 1-bit/cell SLC NAND flash

- 100,000 Program/Erase cycles (with ECC)[1]

- 10 years Data Retention

- 2-bits/cell MLC NAND flash

- 3000-10,000 Program/Erase cycles (with ECC)[2]

- 10 years Data Retention

- 3-bit/cell TLC NAND flash

- 250—500 Program/Erase cycles<sub>[3]</sub>

- 4-bits/cell QLC NAND flash (2011—)

- Developers: Intel, SanDisk, Micron, Toshiba and Samsung

[1] ST Micro-electronics NAND SLC large page datasheet (NAND08GW3B2A) [2] ST Micro-electronics NAND MLC large page datasheet (NAND04GW3C2A) [3] Spectek F??B74A61K3BAA??-AF/L

### Management Issues – Challenges

- The write throughput drops significantly after garbage collection starts!

- The capacity of flash-memory storage systems increases very quickly such that memory space requirements grows quickly.

- Reliability becomes more and more critical when the manufacturing capacity increases!

- The significant increment of flash-memory access rates seriously exaggerates the Read/Program Disturb Problems!

2011/10/10

Tei-Wei Kuo, NTU, All Rights Reserved

2

### Agenda

- Introduction

- Architecture and Design Issues

- Performance Issues

- Reliability/Endurance Issues

- Conclusion

2011/10/10

Tei-Wei Kuo, NTU, All Rights Reserved

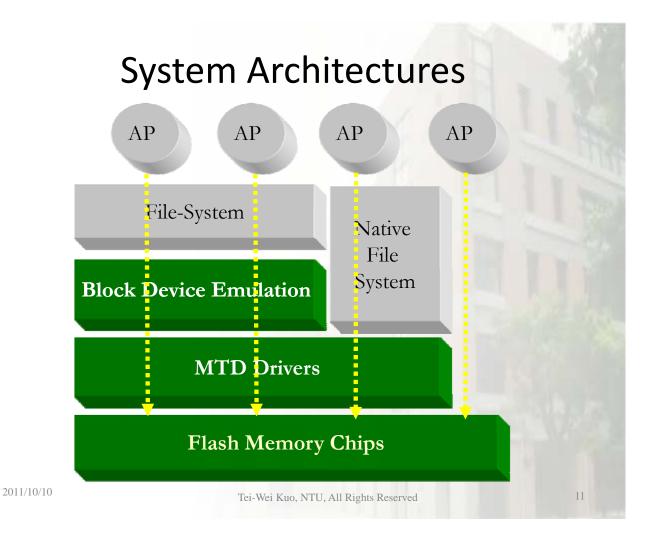

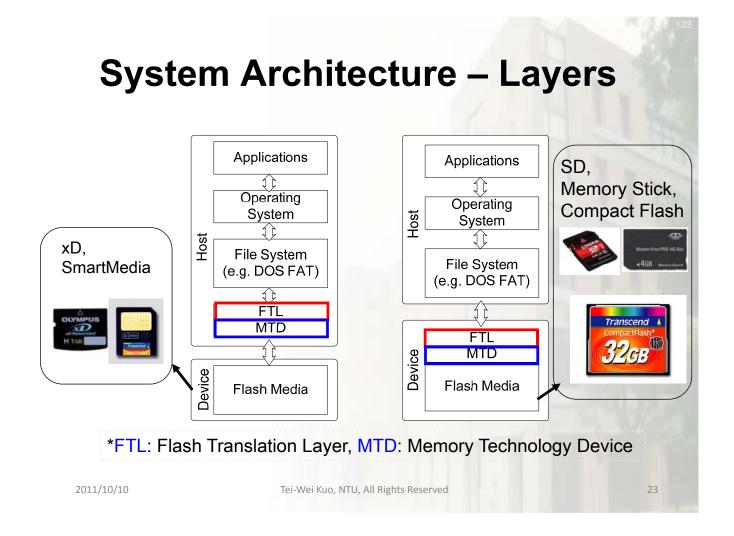

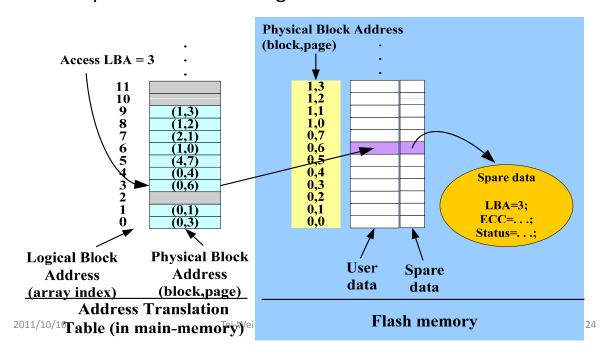

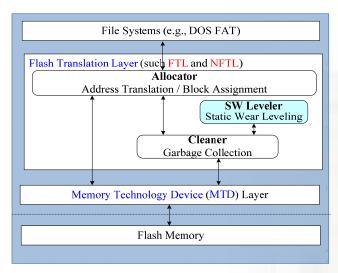

### Example Address-Mapping Policies – FTL

- FTL adopts a page-level address translation mechanism.

- The main problem of FTL is on large memory space requirements for storing the address translation information.

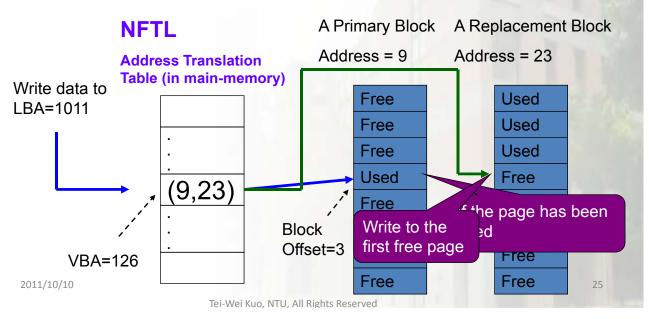

### Example Address-Mapping Policies - NFTL

- A logical address under NFTL is divided into a virtual block address and a block offset.

- e.g., LBA=1011 => virtual block address (VBA) = 1011 / 8 = 126 and block offset = 1011 % 8 = 3

## Address-Mapping Policies – Fine-Grained vs. Coarse Grained Ones

|                             | FTL     | NFTL    |  |

|-----------------------------|---------|---------|--|

| Memory Space Requirements   | Larger  | Smaller |  |

| Address Translation Time    | Shorter | Longer  |  |

| Garbage Collection Overhead | Less    | More    |  |

| <b>Space Utilization</b>    | Higher  | Lower   |  |

- The Memory Space Requirements for a 16GB NAND flash (4KB/Page, 4B/Table Entry, 128 Pages/Block)

- FTL: 16MB (= 4\*16G/4K)

- NFTL: 128KB (= 4\*16G/(4K\*128))

## Key Issues and Technologies

#### Address Translation

- Reduce the size of address translation information

- Adjust address translation scheme with heterogeneous mapping granularities

- Store address translation information over flash

#### Garbage Collection and Wear Leveling

- Cost versus Benefits

- Needs in Performance/Real-time Constraints

#### Parallelism in Access

Adaptive Striping and Architecture Designs

2011/10/10

Tei-Wei Kuo, NTU, All Rights Reserved

2-

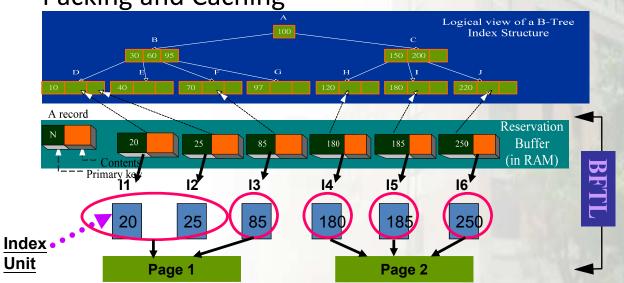

# Address Translation – Indexing and Small Writes

Packing and Caching

#### Flash Translation Layer (FTL)

Source: Chin-Hsien Wu, Li-Pin Chang, and Tei-Wei Kuo, "An Efficient B-Tree Layer Implementation for Flash-Memory Storage Systems," ACM Transactions on Embedded Computing Systems, Volume 6, Issue 3, July 2007

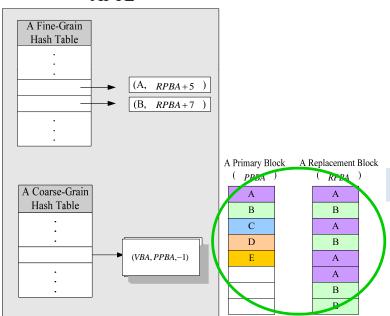

## Address Translation – Adaptive Flash Translation Layer (AFTL)

**AFTL**

- 1. AFTL doesn't erase the two blocks immediately.

- 2. AFTL moves the mapping information of the replacement block to the fine-grained hash table by adding fine-grained slots.

#### Coarse-to-Fine Switching

3. The RPBA field of the corresponding mapping information is nullified.

29

Chin-Hsien Wu and <u>Tei-Wei Kuo</u>, 2006, "An Adaptive Two-Level Management for the Flash Translation Layer in Embedded Systems," IEEE/ACM 2006 International Conference on Computer-Aided Design (ICCAD), November 5-9, 2006.

3/29/2007 Embedded Systems and Wireless Networking Lab.

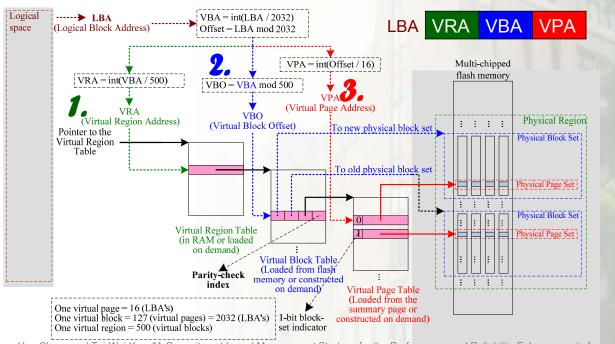

# Address Translation – Region-Based Mapping

A three-level address translation architecture

Yuan-Hao Chang and Tei-Wei Kuo, "A Commitment-based Management Strategy for the Performance and Reliability Enhancement of Flash-memory Storage Systems," the ACM/IEEE Design Automation Conference (DAC), San Francisco, Jul. 26-31, 2009.

Tei-Wei Kuo, NTU, All Rights Reserved

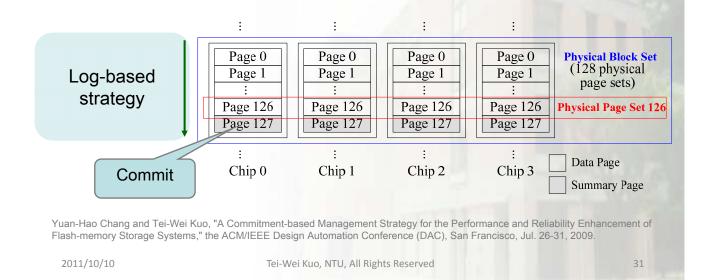

# Address Translation – Commitment-based Management

An adaptive block mapping mechanism with a log-based strategy

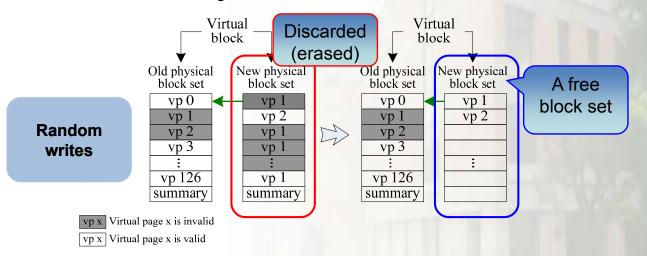

# Address Translation – Adaptivity to Access Patterns

- Good performance to random writes and sequential writes

- A virtual block → up to 2 physical block sets

- Replace the block set with fewer valid data.

- Set the remaining one as the old one.

Yuan-Hao Chang and Tei-Wei Kuo, "A Commitment-based Management Strategy for the Performance and Reliability Enhancement of Flash-memory Storage Systems," the ACM/IEEE Design Automation Conference (DAC), San Francisco, Jul. 26-31, 2009.

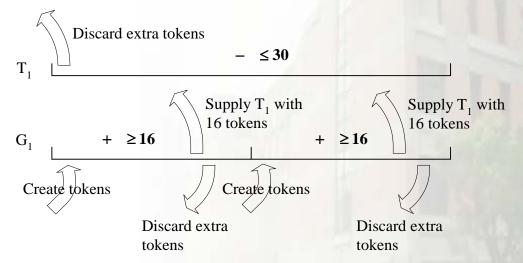

## Garbage Collection – Real-Time Garbage Collection

Garbage Collection and MLC Write Constraints

Source: Li-Ping Chang and Tei-Wei Kuo, "A Real-Time Garbage Collection Mechanism for Flash-Memory Storage Systems in Embedded Systems," the 8th International Conference on Real-Time Computing Systems and Applications (RTCSA), Tokyo, Japan, March 2002

2011/10/10

Tei-Wei Kuo, NTU, All Rights Reserved

33

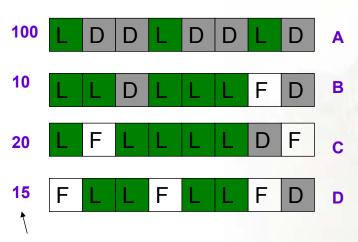

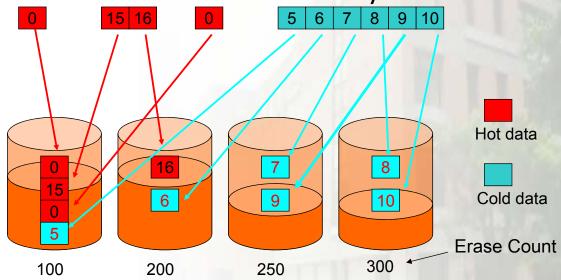

## Parallel access supports – Adaptive striping

Stripping and Utilization:

Distribute hot and cold data evenly over banks

Source: Li-Pin Chang and Tei-Wei Kuo, "An Adaptive Stripping Architecture for Flash Memory Storage Systems

of Embedded Systems," IEEE Eighth Real-Time and Embedded Technology and Applications Symposium (RTAS),

San Jose, USA, Sept 2002

Tei-Wei Kuo, NTU, All Rights Reserved

## Agenda

- Introduction

- Architecture and Design Issues

- Performance Issues

- Reliability/Endurance Issues

- Conclusion

2011/10/10

Tei-Wei Kuo, NTU, All Rights Reserved

35

## Reliability Challenges

- Low Endurance

- Bad Data Retention

Single-Level-Cell (SLC)

- High Bit Error Rate

- Serious Disturbing

Multi-Level-Cell (MLC)<sup>1</sup>

|                                      | Read<br>(Mbps) | Write<br>(Mbps) | Endurability (Erase cycles) | Reliability<br>(Bit error rate) | Cost<br>(US \$/GB) |

|--------------------------------------|----------------|-----------------|-----------------------------|---------------------------------|--------------------|

| SLC <sup>1</sup>                     | 235            | 23              | 60,000                      | 10 <sup>-9</sup>                | 0.813              |

| MLC <sub>x2</sub> <sup>2</sup>       | 109            | 6.3             | ≤ 3,000                     | 10 <sup>-6</sup>                | 0.1134             |

| TLC / MLC <sub>x3</sub> <sup>3</sup> | 27             | 0.8             | ≤ 500                       | ≥10 <sup>-5</sup>               | 0.0955             |

| MPEG-2 (1280x720)                    | 20             | 20              |                             |                                 |                    |

| MPEG-4                               | 6 - 7          | 6 - 7           |                             |                                 |                    |

\* 2010Q2: SLC 6.01USD/GB, MLCx2 1.70USD/GB, TLC 1.49USD/GB [1][2] Micron MT29F256G08AUCAB & MT29F512G08CUAA; [3] Spectek FNNB63A (downgraded flash product); [4][5] DRAMExchange, October 2011

### Wear-Leveling Technologies

Key Issues and Technologies

Tei-Wei Kuo, NTU, All Rights Reserved

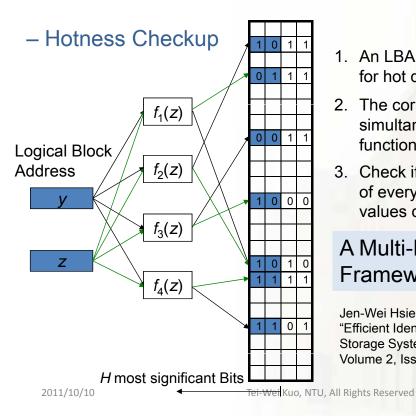

#### Identification of Hot and Cold Data

- Locality in Access

- Garbage Collection Performance

#### Wear Leveling

- Dynamic Wear Leveling

- Static Wear Leveling

#### Reliability Enhancement

- Downgrading Designs

- Reliability Enhancement at FTL/MTD/File-System Levels

2011/10/10

2011/10/10

37

#### Efficient Hot-Data Identification

- 1. An LBA is to be verified as a location for hot data.

- 2. The corresponding LBA *y* is hashed simultaneously by *K* given hash functions.

- Check if the H most significant bits of every counter of the K hashed values contain a non-zero bit value.

## A Multi-Hash-Function Framework

Jen-Wei Hsieh, <u>Tei-Wei Kuo</u>, Li-Pin Chang, "Efficient Identification of Hot Data for Flash Memory Storage Systems," the ACM Transactions on Storage, Volume 2, Issue 1, pp.22-40, Feb 2006.

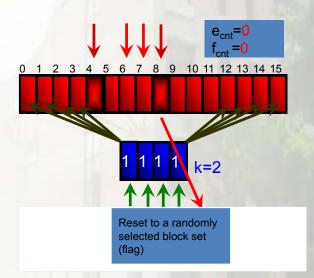

### Static Wear Leveling

- A modular design for compatibility considerations

- An unevenness level (e<sub>cnt</sub> / f<sub>cnt</sub>) >= T → Triggering of the Static Wear Leveler

Yuan-Hao Chang, Jen-Wei Hseuh, and <u>Tei-Wei Kuo</u>, 2007, "Endurance Enhancement of Flash-Memory Storage Systems: An Efficient Static Wear Leveling Design," ACM/IEEE 44-th Design Automation Conference (DAC), San Diego, USA, June 2007. [Best Paper Nomination] 2011/10/10 Tei-Wei Kuo, NTU, All Rights Reserved

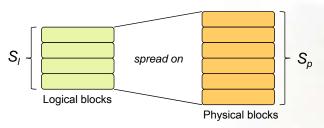

## A Set-Based Mapping Strategy for Downgraded Flash

An efficient set-based mapping strategy is proposed

Yuan-Sheng Chu, Jen-Wei Hsieh, Yuan-Hao Chang, and Tei-Wei Kuo, 2009, "A Set-Based Mapping Strategy for Flash-Memory Reliability Enhancement," the ACM/IEEE 12th Conference of Design, Automation, and Test in Europe (DATE), Nice, France, April 20-24, 2009.

Set Hash Function (SHF)

Set Hash Function (SHF)

Logical Set Table (LST)

Physical Set Table (PST)

Physical Set Table (UIT)

Flash Memory

2011/10/10

Tei-Wei Kuo, NTU, All Rights Reserved

41

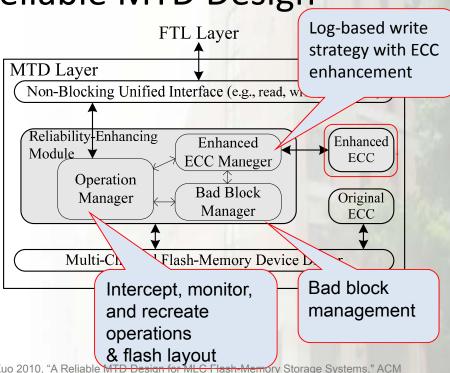

Reliability Enhancement – A Reliable MTD Design

- Segment based

mirroring with

bad block

replacement

- Log-basedwrite strategywith ECCenhancement

Yuan-Hao Chang and <u>Tei-Wei Kuo</u> 2010, "A Reliable MTD Design for MLC Flash-Memory Storage Systems," ACM 20 http://dipnational Conference on Embedded Software (EMSOFT), Scottsdale, Arizona, USA, Oct. 24-29, 2010

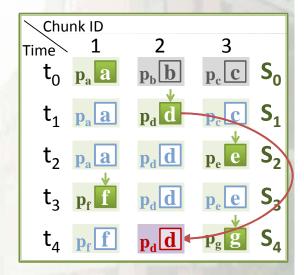

### Reliability Enhancement – Forward Copying in a Native File System

Duplicate data of the latest version of chunks which affected by the invalidation.

## Which chunks need to be forward-copied?

- Consider the co-existent relation

- Chunks whose the latest out-ofdate version only co-exist with the invalidated page.

- Chunks which are latest updated between the time points that the invalidated page and the latest outof-date version.

Pei, Han Hsu, Yuan-Hao Chang, Po-Chun Huang, Tei-Wei Kuo, David Du, "A Version-based Strategy for Reliability Enhancement of Flash File Systems", ACM/IEEE DAC 2011.

### Conclusion

- What Is Happening?

- Solid-State Storage Devices

- New Designs in the Memory Hierarchy

- Flash-Powered Storage Servers

- More Applications in Components and Products

- Challenging Issues: Performance, Cost, and Reliability

- Scalability Technology

- Reliability Technology

- Customization Technology

#### **Contact Information**

#### Professor Tei-Wei Kuo

- ktw@csie.ntu.edu.tw

- URL: http://csie.ntu.edu.tw/~ktw

- Flash Research: http://newslab.csie.ntu.edu.tw/~flash/

- Office: +886-2-23625336-257

- Fax: +886-2-23628167

- Address:

Dept. of Computer Science & Information Engr. National Taiwan University, Taipei, Taiwan 106

2011/10/10

Tei-Wei Kuo, NTU, All Rights Reserved

15

## Questions or Comments?