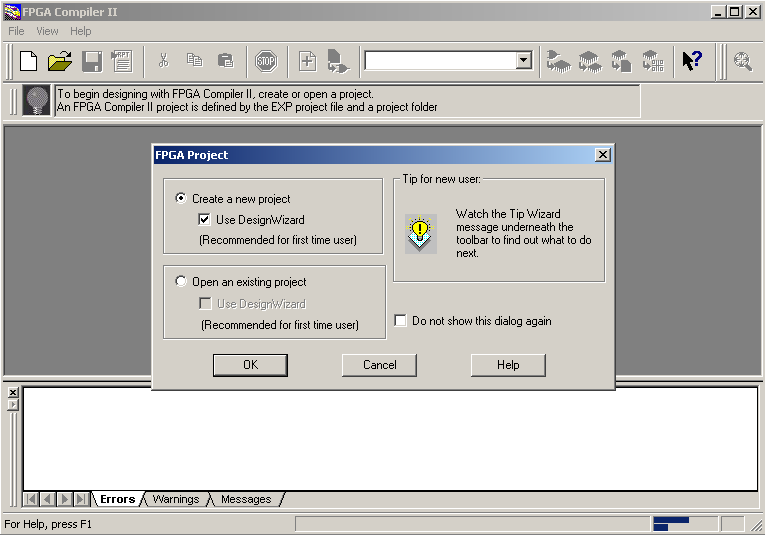

2. Select the default Design Wizard project

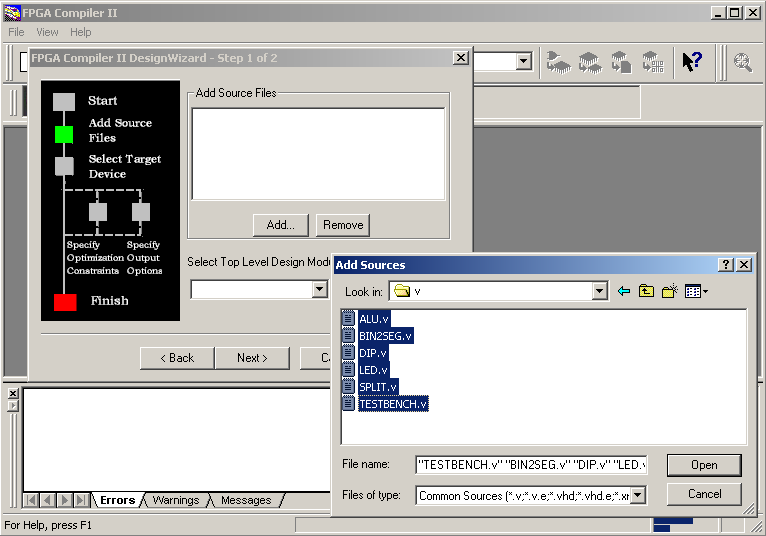

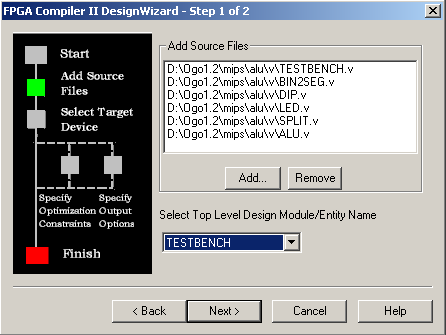

3. Select the Verilog files for the ALU project

4. Select the toplevel design module (TESTBENCH)

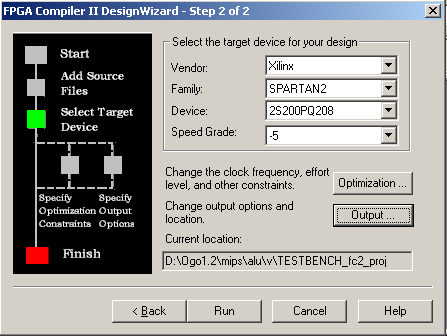

5. Enter the parameters of the target FPGA device and press

Run

Note that the FPGA you are using can be different from the one

shown on this figure. Check your type!

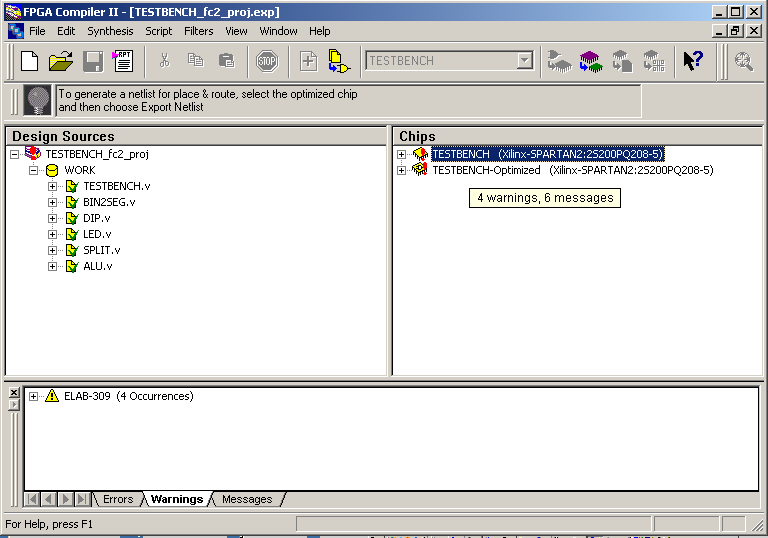

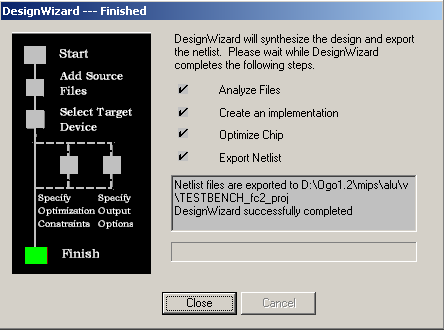

6. After the compilation is finished, you can examine the error

and warning messages by clicking on the output chips (TESTBENCH and

TESTBENCH-Optimized) and examining the output window (bottom of the

screen)